# NorthStar HSIO-4 HORIZON Serial Input/OutputFour Port USER/TECHNICAL MANUAL

# HSIO-4 HORIZON Serial Input/Output — Four Port USER/TECHNICAL MANUAL

HORIZON® is a registered trademark of North Star Computers, Inc.

Copyright © 1981, by North Star Computers, Inc.

All Rights Reserved

00187B

### TABLE OF CONTENTS

| SECTION 1 | GENERAL INFORMATION                                          | PAGE |

|-----------|--------------------------------------------------------------|------|

|           | 1.1 Introduction                                             | 1    |

|           | 1.2 Warranty                                                 | 2    |

|           | 1.3 Features of the HSIO-4                                   | 3    |

|           |                                                              |      |

| SECTION 2 | INSTALLING THE HSIO-4                                        |      |

|           | 2.1 Unpacking the HSIO-4                                     | 4    |

|           | 2.2 Setting I/O Address Switches for<br>the North Star TSS/A | 5    |

|           | 2.3 Configuration Changes                                    | 6    |

|           | 2.4 Completing Installation                                  | 7    |

|           |                                                              |      |

| SECTION 3 | IMPLEMENTING HSIO-4 FEATURES                                 | 14   |

|           | 3.1 General Concepts                                         | 14   |

|           | 3.1.1 Establishing a Communication Link                      | 15   |

|           | 3.1.2 HSIO-4 Board Layout                                    | 19   |

|           | 3.1.3 I/O Addresses                                          | 20   |

|           | 3.1.4 Interrupts                                             | 22   |

|           | 3.2 Asynchronous Operation                                   | 24   |

|           | 3.2.1 Configuring Port as Modem                              | 24   |

|           | 3.2.2 Configuring Port as Terminal                           | 25   |

|           | 3.2.3 Baud Rate Selection                                    | 26   |

|           | 3.2.4 Sample Program                                         | 29   |

|           | 3.2.5 Current Loop Operation                                 | 33   |

|           | 3.2.6 Buffer Full Signals                                    | 35   |

|     |                                                | PAGE |

|-----|------------------------------------------------|------|

| 3.3 | Synchronous Operation                          | 38   |

|     | 3.3.1 Fixed Baud Rate of 55.8KHz               | 39   |

|     | A. Configuring Port as Modem                   | 39   |

|     | B. Configuring Port as Terminal                | 40   |

|     | 3.3.2 Programmable Baud Rates                  | 41   |

|     | A. Configuring Port as Modem                   | 41   |

|     | B. Configuring Port as Terminal                | 42   |

|     | 3.3.3 Programming Baud Rates                   | 43   |

|     | 3.3.4 Alternative Baud Rates                   | 45   |

|     | 3.3.5 Sample Program                           | 46   |

|     |                                                |      |

| 3.4 | Interrupts                                     | 50   |

|     | 3.4.1 Arming and Disarming Maskable Interrupts | 51   |

|     | 3.4.2 Arming the Synchronous Detect Interrupt  | 53   |

|     | 3.4.3 Connecting the Interrupt Lines           | 54   |

¥ .

|            |                                                                             | PAGE |

|------------|-----------------------------------------------------------------------------|------|

| SECTION 4  | THEORY OF OPERATION .                                                       | 56   |

|            | 4.1 Address Decoder                                                         | 57   |

|            | 4.2 Data Buffers                                                            | 58   |

|            | 4.3 Baud Rate Generator                                                     | 58   |

|            | 4.4 Interrupt Header                                                        | 59   |

|            | 4.5 I/O Port                                                                | 60   |

|            | 4.5.1 USART                                                                 | 61   |

|            | 4.5.2 Configuration and Clock Headers                                       | 61   |

|            | 4.5.3 Baud Rate Select Register                                             | 62   |

|            | 4.5.4 Interrupt Select Register                                             | 63   |

|            |                                                                             |      |

| SECTION 5  | TROUBLESHOOTING                                                             | 64   |

|            | 5.1 Creating a Test Diskette                                                | 65   |

|            | 5.1.1 Creating an Auto-Start DOS Diskette                                   | 65   |

|            | 5.1.2 Creating the Test Program                                             | 66   |

|            | 5.1.3 Configuring Basic for Auto-Start<br>Operation                         | 68   |

|            | 5.2 Software Testing                                                        | 69   |

|            | 5.3 Oscilloscope Testing                                                    | 71   |

|            | 5.4 Repair Procedures                                                       | 73   |

|            |                                                                             |      |

| APPENDICES |                                                                             |      |

|            | A. RS-232 Connector Pin Assignments                                         | 74   |

|            | B. Notes On The Interface To The USART and USART Manufacturer Specification | 75   |

|            | C. HSIO-4 Parts List                                                        | 92   |

|            | D. Schematic Drawings                                                       | 94   |

|            |                                                                             |      |

### 1.1 INTRODUCTION

The HSIO-4 is a 4-port serial input/output board designed for use with the HORIZON. It can also be used with some other S-100 bus systems.

This manual provides basic instructions on how to install the HSIO-4 board in your HORIZON; it also provides technical information and detailed instructions for implementing a range of HSIO-4 features and operating characteristics.

SECTION 1 describes HSIO-4 features and capabilities and contains warranty information.

SECTION 2 provides basic instructions on how to unpack and install the HSIO-4 board in a HORIZON.

SECTION 3 describes interface connections and requirements; it also provides detailed instructions on how to use the HSIO-4 to establish communication links between the HORIZON and a variety of peripheral devices.

SECTION 4 provides a functional block diagram of the HSIO-4 and discusses the theory of operation.

SECTION 5 provides troubleshooting procedures to aid in isolating problems.

The APPENDICES furnish detailed technical information, including schematic drawings, RS-232 pin assignments, and a manufacturer data sheet for the USART.

Every effort has been made to ensure the accuracy of this manual. If you find errors or omissions in this material or if you have suggestions on how it can be improved, please write:

North Star Computers, Inc.

North Star Technical Services Group

14440 Catalina Street

San Leandro, CA 94577

### 1.2 WARRANTY

North Star Computers, Inc., warrants the electrical and mechanical parts and workmanship of this product to be free of defects for a period of 90 days from date of purchase. If such defects occur, North Star Computers, Inc., will repair the defect at no cost to the purchaser. This warranty does not extend to defects resulting from improper use or assembly by purchaser, nor does it cover transportation to the factory. Also, the warranty is invalid if all instructions included in the accompanying documentation are not carefully followed.

Should a unit returned for warranty repair be deemed by North Star Computers, Inc. to be defective due to purchaser's action, then a repair charge (not to exceed \$50 without purchaser's consent) will be assessed. ANY UNIT(S) OR PART(S) RETURNED FOR WARRANTY REPAIR MUST BE ACCOMPANIED BY A DATED COPY OF THE ORIGINAL SALES RECEIPT. The item should be returned to the dealer from whom the product was purchased, for implementation of the warranty. When sending the item to the factory for repair, the dealer must call the North Star Technical Hotline to receive a Return Material Authorization (RMA) number to accompany the item to the factory. Terminals and printers are covered under separate warranties.

The following warranty limitation applies to units located outside the United States of America: All costs and arrangements for transportation of the product to and from the factory are borne entirely by the customer.

No warranty, expressed or implied, is extended concerning completeness, correctness, or suitability of the North Star equipment for any particular application. There are no warranties which extend beyond those expressly stated herein. This limited warranty is made in lieu of all other warranties, expressed or implied, and is limited to repair or replacement of the product.

# 1.3 FEATURES OF THE HSIO-4

The HSIO-4 is a 4-port serial input/output board designed by North Star Computers, Inc., for use with the HORIZON and North Star multi-user systems. As supplied, the HSIO-4 is configured for use with the North Star TSS/A Multi-User System for Application Software. Additional capabilities provide flexibility and permit operation in a variety of hardware and software environments.

### Synchronous/Asynchronous

The HSIO-4 provides four serial input/output ports which may be configured for synchronous or asynchronous communications.

### Baud Rate Selection

Baud rates are programmable and may be selected from among ten available asynchronous baud rates and five available synchronous baud rates. Simple wiring changes provide additional baud rates.

Asynchronous Range: 75 baud to 19.2K baud Synchronous Range: 1.76K baud to 55.8K baud

### Mode Configuration

All four ports use RS-232 signal levels. A hardware change permits 20mA current loop operation. As supplied, each port is wired for connection to a standard terminal or printer. Each port has a configuration header which may be changed to permit connection to a modem or another computer.

### Buffer Full Signals

The HSIO-4 accommodates printers and other peripheral devices using 'buffer full' signals.

### Interrupts

Each port provides four sources of interrupt; three are maskable, the fourth is armed by a jumper. The resultant interrupt from each port may be connected to any of the S-100 bus interrupt lines.

### 2.1 UNPACKING THE HSIO-4

The HSIO-4 board is shipped in a carton containing:

- 1. North Star HSIO-4 board

- 2. Four ribbon cables

- Plastic envelope containing eight jackscrews, lockwashers, and nuts.

- 4. HSIO-4 User/Technical Manual

Examine the contents of the carton to make sure they match this list. If anything appears to be damaged due to shipping, please notify your dealer immediately.

### CAUTION

Before handling the board, you should ground yourself to discharge whatever static electricity may have built up on your body. The electronic components on the board are sensitive to static electricity. So, just before you handle the board, touch a grounded metal object, such as the chassis of a HORIZON that is plugged into a wall outlet. This will prevent a surge of static electricity from damaging the components.

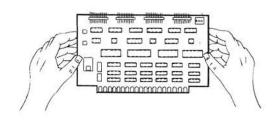

When handling the board, touch it only by the edges to avoid bending pins on the components. If you lay the board down, put it on a flat surface with the components facing up.

Figure 2-1

# 2.2 SETTING I/O ADDRESS SWITCHES FOR THE NORTH STAR TSS/A

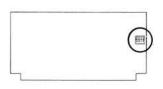

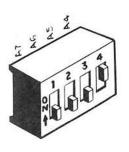

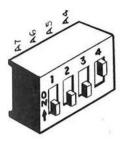

As supplied, the I/O address switches on the HSIO-4 board are set for use with the North Star TSS/A (Multi-User System for Application Software). The I/O addresses for each port are set by the four switches located in the upper right corner of the board.

Figure 2-2

Figure 2-3

To make sure the switches have not been inadvertently changed, check them against the setting shown in Figure 2-3.

If you are using different software, refer to Section 3 for instructions on how to set the I/O address switches.

# 2.3 CONFIGURATION CHANGES

As supplied, the HSIO-4 is ready for immediate connection to four asynchronous RS-232 terminals or printers.

If you are using the North Star TSS/A Multi-User System for Application Software with asynchronous RS-232 terminals and printers, the HSIO-4 can be installed directly in the HORIZON without modification.

If you are using different software or using hardware with different operating characteristics, you may need to implement configuration changes and/or programming routines and should refer to Section 3 (IMPLEMENTING HSIO-4 FEATURES) for general guidelines and specific instructions before continuing this installation procedure.

### IMPORTANT NOTE

Any necessary configuration changes must be completed BEFORE installing the HSIO-4 board in the HORIZON.

### WARNING

Turn off the power switch on the back of the HORIZON, and unplug the power cord from the wall outlet before you remove the HORIZON cover. The high voltages used in the computer can be dangerous unless you observe this precaution.

Do NOT remove the cover from the HORIZON until the power is off, the fan has stopped, and the red indicator light on the front panel has fully dimmed.

Remove the four screws that hold the HORIZON cover in place. Lift off the cover.

Hold the HSIO-4 board in one hand and touch the metal chassis of the HORIZON with the other hand. This will eliminate any difference in static potential between the HSIO-4 board and the computer.

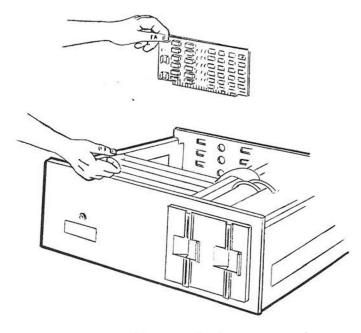

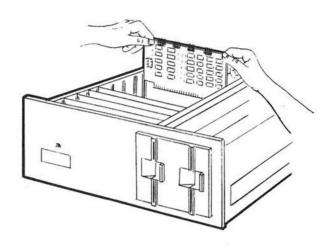

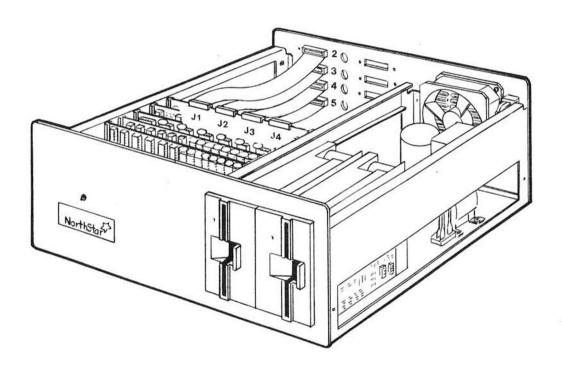

Figure 2-4

Hold the board as shown in figure 2-5, with the component side of the board toward the front of the HORIZON. Slide the board into the rear-most slot in the card cage. If that slot is already occupied by another board, remove that board and place it in an unused slot.

Figure 2-5

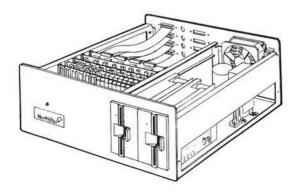

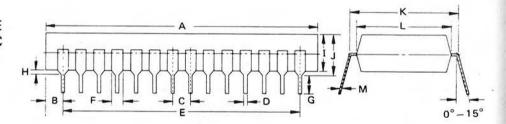

The row of metallic strips or "fingers" on the bottom of the board should fit into the connector at the base of the slot. Press firmly on the top of the board to make sure it is fully seated in the connector. The top of the HSIO-4 board should be even with the other installed North Star boards.

If a second HSIO-4 board is utilized, it should be installed in the slot immediately in front of the first HSIO-4 board.

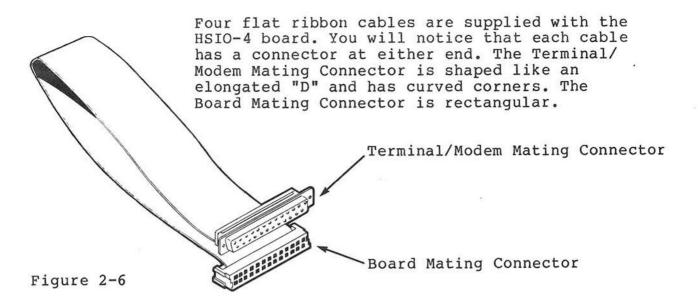

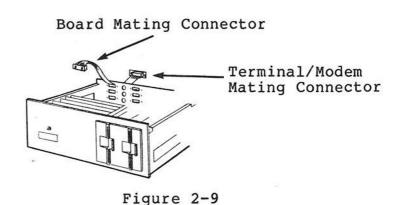

Each Board Mating Connector must be plugged into one of the four port connectors on the HSIO-4; each Terminal/Modem Mating Connector must be seated in one of the connector holes in the back panel of the HORIZON.

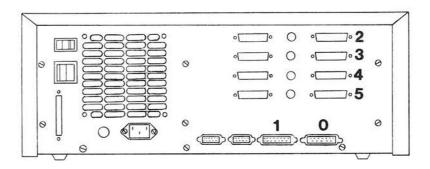

It is recommended that you utilize the outer-most column of connector holes, as shown in Figure 2-7. The other column of connector holes should be utilized only if a second HSIO-4 board is installed.

Figure 2-7

Before connecting the cables, you should number each connector hole on the HORIZON back panel. For use with the TSS/A, the connector holes should be numbered as shown in Figure 2-8.

Figure 2-8

From outside the back panel of the HORIZON, thread each ribbon cable -- rectangular Board Mating Connector first -- through a connector hole. Gently pull the cable through until the Terminal/Modem Mating Connector touches the sides of the hole. From outside the back panel, push firmly to seat the connector in the hole.

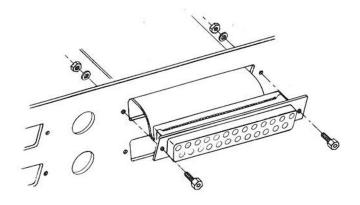

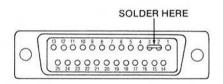

Using the jackscrews provided, bolt the D-connector in place, as shown in Figure 2-10. From outside the back panel, insert each screw through the connector mounting. Slip a lockwasher over the screw, and secure it with a nut.

Repeat these installation procedures for all four ribbon cables.

Figure 2-10

Taking care not to twist the cables, plug each Board Mating Connector into the appropriate 26-pin header at the top of the HSIO-4 board. See Figure 2-11. For use with the TSS/A, the cables should be connected as follows:

J1 to Port 2 J2 to Port 3 J3 to Port 4 J4 to Port 5

Figure 2-11

Gently flex each cable to fit it into the space between the card cage and the back panel, taking care to position the cables so they will not be crushed when you replace the lid.

Replace the cover on the HORIZON, and replace the screws.

Connect the terminals and/or printers to the appropriate I/O port sockets on the HORIZON back panel.

Plug the HORIZON line cord into the wall outlet. Plug the power cords for all connected terminals into the wall outlet. Turn on the power switches for the HORIZON and all terminals.

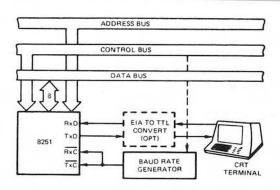

This section provides an overview of serial data communication between computers and other electronic devices; it also provides detailed instructions on how to use the HSIO-4 to establish communication links between the computer and a variety of periperal devices.

As supplied, the HSIO-4 is ready for immediate connection to four asynchronous RS-232 terminals or printers. Connection to most asynchronous terminals and printers usually requires no configuration changes to the HSIO-4. Reading through the discussion that follows can help you to determine what, if any, changes are required by the particular hardware and software you are using. Once you have identified the needed modifications, you should consult the appropriate subsection for specific, detailed instructions.

### 3.1 GENERAL CONCEPTS

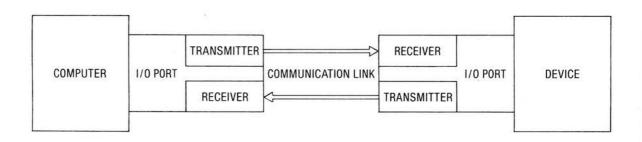

In order to transmit data between a computer and another electronic device, a communication link must be established. Such a communication link is usually comprised of a cable with a connecting plug at each end. One plug is connected to an Input/Output (I/O) port in the computer; the other is connected to an I/O port in the electronic device.

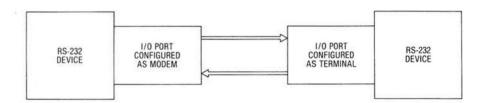

Figure 3-1

# 3.1.1 ESTABLISHING A COMMUNICATION LINK

To establish a communication link between two electronic devices (such as a computer and a terminal), the operating characteristics of both devices must be compatible.

The HSIO-4 has four serial I/O ports. Each I/O port provides the interface necessary to establish a communication link between a HORIZON computer and another electronic device with a compatible serial I/O port.

### RS-232 OR 20mA CURRENT LOOP SIGNALS

Most computers, terminals, and printers use RS-232 signals. A few commercially used terminals, such as teletypes, use 20mA current loop signals.

As supplied, each HSIO-4 port is wired to use RS-232 signals. 20mA current loop signals can be accommodated with a configuration change. Refer to section 3.2.5 for specific instructions.

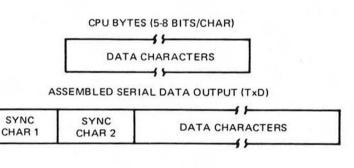

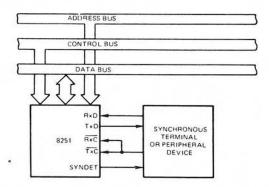

### ASYNCHRONOUS OR SYNCHRONOUS TRANSMISSION

Each port on the HSIO-4 allows two different types of data transmission: asynchronous and synchronous. Typical communication between a computer and a terminal is asynchronous. Synchronous communication is used primarily to facilitate high-speed computer-to-computer data transmission.

### ASYNCHRONOUS

See Section 3.2 for specific configuration and programming instructions. As supplied, each port on the HSIO-4 is configured for asynchronous operation.

### SYNCHRONOUS

To operate an I/O port in synchronous mode, you must wire the Configuration Header and the Clock Header, and then program the I/O port according to the specific procedures in Section 3.3.

### TERMINAL OR MODEM

To establish an RS-232 communication link between two electronic devices, one device must simulate a modem; the other must simulate a terminal. As supplied, each HSIO-4 port simulates a modem.

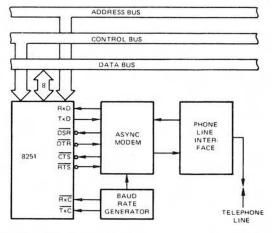

Figure 3-2

COMPUTER TO TERMINAL COMMUNICATION

If the HORIZON is to communicate with a serial

terminal (such as a video terminal or a

printer), the interfacing port on the HSIO-4

must be configured to simulate a modem.

COMPUTER TO MODEM COMMUNICATION

If the HORIZON is to communicate with a modem or acoustic coupler, the interfacing port on the HSIO-4 must be configured to simulate a terminal. As supplied, each port is configured to simulate a modem. To configure an HSIO-4 port as a terminal, you must wire the Configuration Header for the relevant port according to the specific procedures in Section 3.2.2 for asynchronous operation or Section 3.3 for synchronous operation.

COMPUTER TO COMPUTER COMMUNICATION

The HORIZON can communicate with another computer if one computer simulates a modem while the other simulates a terminal. As supplied, each port on the HSIO-4 board is configured to simulate a modem; it is ready to communicate with a computer that simulates a terminal.

Conversely, to establish a communication link between the HORIZON and another computer that simulates a modem, you must configure an HSIO-4 port to simulate a terminal. To configure an HSIO-4 port as a terminal, you must wire the Configuration Header for the relevant port according to the specific procedures in Section 3.2.2 for asynchronous operation or Section 3.3 for synchronous operation.

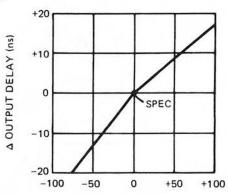

### BAUD RATE

The data transmission speed (baud rate) of the two communicating devices must be the same. Baud rates for each port can be programmed independently to a range of commonly used baud rates. For a list of available baud rates and specific programming instructions, refer to Section 3.2.3 for asynchronous operation, or Section 3.3.2 for synchronous operation.

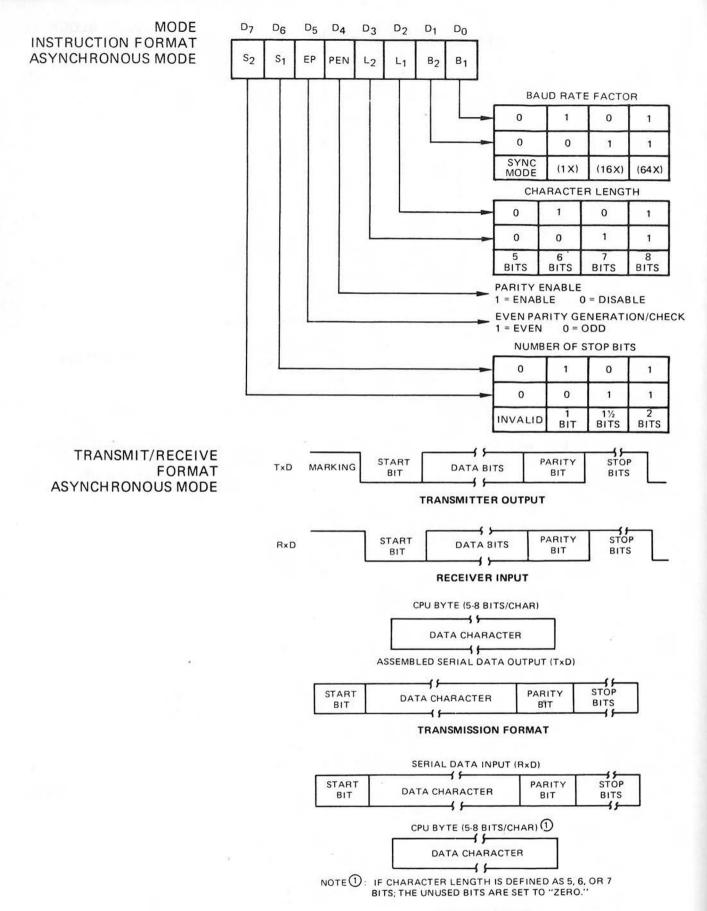

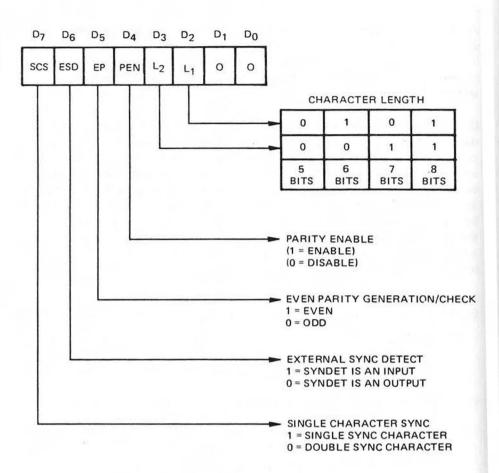

### FORMAT CONVENTIONS

Both communicating devices must use compatible format conventions. Format conventions include: the number of data bits per character, the type of parity, the baud rate factor (lx, l6x, or 64x), the number of stop bits per character (for asynchronous operation) and the sync character(s) (for synchronous operation).

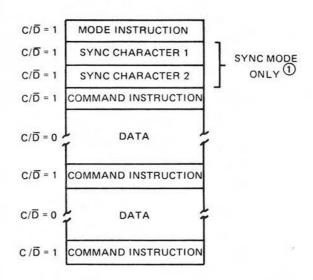

Format conventions are established by programming the USART, which can accomodate a variety of conventions. Software (such as the North Star TSS/A) that has been written specifically for use with the HSIO-4 contains USART initialization routines, which define and establish the required format conventions. For the convenience of the programmer writing software for the HSIO-4, a

sample USART initialization routine that establishes a commonly used set of format conventions is printed in Section 3.2.4 (asynchronous) and Section 3.3.5 (synchronous). In addition, the complete manufacturer specification for the USART is reproduced in Appendix B, along with notes on the interface to the USART.

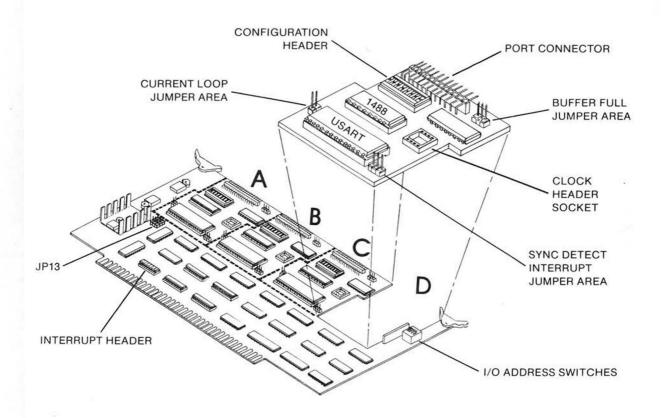

### 3.1.2 HSIO-4 BOARD LAYOUT

Before proceeding to implement any of the features treated in this section, please note:

The four ports on the HSIO-4 board are identically arranged; they are labeled alphabetically from left to right as shown below.

Figure 3-3

### 3.1.3 I/O ADDRESSES

The HSIO-4 requires 16 consecutive I/O addresses. (All addresses referenced in this section are I/O addresses.) Each of the four ports uses four consecutive addresses. Addresses start at XOH and run to XFH. (X represents a hexadecimal digit which is set by switches on the board.)

As can be seen in Table 3-1, port A starts at XOH; port B starts at X4H; port C starts at X8H; port D starts at XCH. The board address space is used as follows:

Table 3-1

I/O PORT ADDRESS ASSIGNMENTS

| Port   | Address | Function             | Port Access |

|--------|---------|----------------------|-------------|

| A      | хон     | Baud rate select     | write only  |

| A      | XIH     | Interrupt mask set   | write only  |

| A      | X2H     | USART data           | read/write  |

|        |         | USART status/control | read/write  |

| A      | хзн     | USART Status/Control | read/write  |

| В      | X4H     | Baud rate select     | write only  |

| В      | х5н     | Interrupt mask set   | write only  |

| В      | хбн     | USART data           | read/write  |

| В      | х7н     | USART status/control | read/write  |

| С      | х8н     | Baud rate select     | write only  |

| C<br>C | х 9 н   | Interrupt mask set   | write only  |

| С      | XAH     | USART data           | read/write  |

| С      | XBH     | USART status/control | read/write  |

| D      | хсн     | Baud rate select     | write only  |

| D      | XDH     | Interrupt mask set   | write only  |

| D      | XEH     | USART data           | read/write  |

| D      | XFH     | USART status/control |             |

|        | AF II   |                      | read, write |

Figure 3-4

Figure 3-5

The hexadecimal digit X used as part of the I/O address is set by the four switches located in the upper right corner of the board (Location 8B).

The four switches yield a total of 16 possible switch settings; each switch setting selects a starting address for the I/O board. Unless otherwise directed by the software manual you are using, use the switch setting illustrated in Figure 3-5 at left, which sets the starting address at 10H.

If the software you are using requires a different starting address, consult Table 3-2 below for the switch setting that corresponds to the required starting address.

Table 3-2

### I/O ADDRESS SWITCH SETTINGS

0 = Off 1 = On

| Starting<br>Address | Swit      | ch Num | ber |    | Reserved Address Regions                                 |

|---------------------|-----------|--------|-----|----|----------------------------------------------------------|

|                     | <u>A7</u> | A6     | A5  | A4 |                                                          |

| 00H                 | 0         | 0      | 0   | 0  | Used by the HORIZON motherboard                          |

| 10H                 | 0         | 0      | 0   | 1  | 35355446 5 1                                             |

| 20H                 | 0         | 0      | 1   | 0  |                                                          |

| 30H                 | 0         | 0      | 1   | 1  |                                                          |

| 40H                 | 0         | 1      | 0   | 0  |                                                          |

| 50H                 | 0         | 1      | 0   | 1  |                                                          |

| 60H                 | 0         | 1      | 1   | 0  | Reserved for North Star use                              |

| 70H                 | 0         | 1      | 1   | 1  | Reserved for North Star use                              |

| 80H                 | 1         | 0      | 0   | 0  | CLERA DEM DISSING CONTROL MANAGEMENT NAME AND ASSESSMENT |

| 90H                 | 1         | 0      | 0   | 1  |                                                          |

| AOH                 | 1         | 0      | 1   | 0  |                                                          |

| вон                 | 1         | 0      | 1   | 1  |                                                          |

| СОН                 | 1         | 1      | 0   | 0  | Used by North Star RAM boards                            |

| D0H                 | 1         | 1      | 0   | 1  |                                                          |

| EOH                 | 1         | 1      | 1   | 0  |                                                          |

| FOH                 | 1         | 1      | 1   | 1  |                                                          |

### 3.1.4 INTERRUPTS

In a multi-user environment, interrupts relieve the processor of the task of polling each peripheral device to see if it is ready to transmit or receive data. Different events generate different interrupt requests. One interrupt request, for example, is generated when the USART has finished sending a byte and is ready to send another; another interrupt request is generated when a byte is ready to be received by the processor.

Each HSIO-4 port provides four interrupt sources. Three may be armed and disarmed under program control; the fourth, Synchronous Detect, is armed by a jumper on the HSIO-4 board. Consult Section 3.4 for instructions on how to program the interrupts and connect interrupt sources to the S-100 bus interrupt lines.

To establish a communication link between two electronic devices, one device must simulate a modem while the other simulates a terminal. If the HORIZON is to communicate with a serial terminal (such as a video terminal, a teletype, or a printer), then the relevant HSIO-4 port must be configured to simulate a modem. Similarly, if the HORIZON is to communicate with a modem, then the relevant HSIO-4 port must simulate a terminal.

# 3.2.1 CONFIGURING PORT AS MODEM

As supplied, each port on the HSIO-4 is configured as a modem; it is ready for connection to an RS-232 terminal. If a port has ever been reconfigured as a terminal, it can be restored to its original configuration as follows:

Remove the Clock Header (if there is one present) from the Clock Header socket.

Please Note: As supplied, Clock Headers are not installed on the HSIO-4 board. However, if a port has been configured for synchronous operation, then a Clock Header will have been installed and must now be removed.

2. Check the shunt in the Configuration Header socket; it should have the following pins connected. (If the original shunt is no longer available, then make up a header with the same connections.)

| pin | 1 | to | pin | 16 |

|-----|---|----|-----|----|

| pin | 2 | to | pin | 15 |

| pin | 3 | to | pin | 14 |

| pin | 4 | to | pin | 13 |

| pin | 5 | to | pin | 12 |

| pin | 6 | to | pin | 11 |

| pin | 7 | to | pin | 10 |

| pin | 8 | to | pin | 9  |

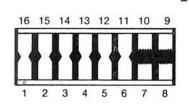

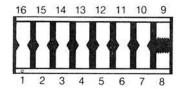

Figure 3-6

# 3.2.2 CONFIGURING PORT AS TERMINAL

If the HORIZON is to communicate with a modem (or with another computer simulating a modem), the interfacing HSIO-4 port must be configured to simulate a terminal.

Configure an HSIO-4 port as a terminal as follows:

Carefully remove the shunt from the Configuration Header socket and replace it with a 16-pin header wired as follows:

pin 1 to pin 2 pin 3 to pin 4 pin 5 to pin 6 pin 7 to pin 10 pin 8 to pin 9 pin 11 to pin 12 pin 13 to pin 14 pin 15 to pin 16

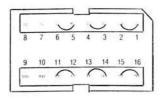

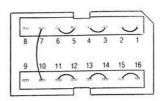

Figure 3-7

Remove the Clock Header (if there is one present) from the Clock Header socket.

Please Note: As supplied, Clock Headers are not installed on the HSIO-4 board. However, if a port has been configured for synchronous operation, then a Clock Header will have been installed and must now be removed.

### 3.2.3 BAUD RATE SELECTION

The baud rate for each HSIO-4 port is programmable and can be selected from among a total of ten available asynchronous baud rates. See Table 3-3 below.

| Table        | 3-3  |       |  |

|--------------|------|-------|--|

| ASYNCHRONOUS | BAUD | RATES |  |

| Output<br>Value | Standard                                | Alternatives<br>(With Jumper Change) |

|-----------------|-----------------------------------------|--------------------------------------|

|                 | 10 (00000000000000000000000000000000000 |                                      |

| 00H             | 19200                                   |                                      |

| 01H             | 9600                                    |                                      |

| 02H             | 4800                                    |                                      |

| 03H             | 2400                                    | 1200 or 150 or 75                    |

| 04H             | 1200                                    | 2400 or 75                           |

| 05H             | 600                                     |                                      |

| 06H             | 300                                     |                                      |

| 07H             | 110                                     |                                      |

The eight "standard" baud rates in Table 3-3 can be program-selected without jumper changes. Jumper changes can make the "alternative" baud rates available for program selection. (For specific instructions, see Section 3.2.3 B.)

### A. PROGRAMMING BAUD RATE SELECTION

The baud rate for each port is programmed independently. To program the desired baud rate for a port, output the Output Value (from Table 3-3) to the Baud Rate Select Address for the relevant port.

To determine the Baud Rate Select Address, consult Tables 3-1 and 3-2 (in Section 3.1.3).

FOR EXAMPLE: Assuming the HSIO-4 board is addressed starting at 10H, you would set the baud rate to 300 on port B by outputting 06H (the Output Value) to I/O address 14H with the following instructions:

0000 3E06 MVI A,6 ; Output Value for 300 Baud Async. 0002 D314 OUT 14H

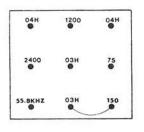

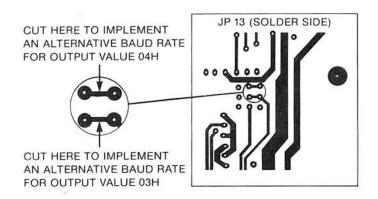

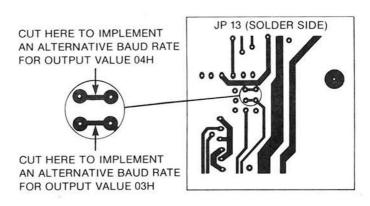

### B. ALTERNATIVE BAUD RATES (REQUIRED JUMPER CHANGES)

The baud rates listed in Table 3-3 as requiring a jumper change can be made available as described below. Please Note: Such a jumper change will affect all four ports.

- Locate JP13, turn the board so that the solder side faces up, and cut one of the traces as directed below.

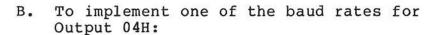

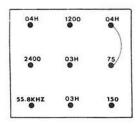

- A. To implement one of the baud rates for Output Value 03H:

Cut the bottom trace, as shown in Figure 3-9. Then turn the board so that the component side faces up, and install a mini-jump between the pin marked with the speed you wish to specify and the nearest pin marked "03H." Figure 3-8, for example, shows where to install the mini-jump to specify 150 baud.

Figure 3-8

Figure 3-9

Cut the top trace, as shown in Figure 3-9. Then, turn the board so that the component side faces up and install a mini-jump between the pin marked with the speed you wish to specify and the nearest pin marked "04H." Figure 3-10, for example, shows where to install the mini-jump to specify 75 baud.

Figure 3-10

### 3.2.4 SAMPLE PROGRAM

This section provides an example of how to program the four HSIO-4 ports for use with four asynchronous RS-232 terminals and/or printers. Programming other configurations requires a detailed familiarity with USART operation. For the convenience of the programmer, a complete manufacturer data sheet for the USART is reproduced in Appendix B.

### The following sample program:

- checks input status and inputs a character for each of the four ports;

- checks output status and outputs a character for each of the four ports;

- 3. initializes the HSIO-4 board.

### Nine routines are given:

CINA inputs a character from port A CINB inputs a character from port B CINC inputs a character from port C CIND inputs a character from port D

COUTA outputs a character to port A COUTB outputs a character to port B COUTC outputs a character to port C COUTD outputs a character to port D

INIT initializes the HSIO-4 board

```

0000

; Sample asynchronous I/O routines for HSIO-4

0000

0000

0010

BASE

EOU

:Address of HSIO-4

10H

EOU

0010

PORTA

BASE+00H

; Address of port A

0014

EOU

PORTB

BASE+04H

; Address of port B

0018

PORTC

EOU

BASE+08H

;Address of port C

001C

PORTD

EOU

BASE+0CH

; Address of port D

0000

î

0001

BAUDA

EOU

1

;Baud rate for port A of 9600

0001

BAUDB

EOU

1

;Baud rate for port B of 9600

0001

BAUDC

EQU

1

;Baud rate for port C of 9600

1

0001

BAUDD

EOU

;Baud rate for port D of 9600

0000

0000

0

BAUD

EOU

;Baud rate set

0001

MADK

1

EOU

; Interrupt mask set

2

0002

UDAT

EQU

; USART data

0003

USTA

EQU

3

;USART status

0000

;

0000

;

0000

; Port A input and output routines

0000

0000

DB13

CINA

IN

PORTA+USTA

; Check USART status

0002

E602

ANI

2

;Get RxReady bit

0004

28FA

JRZ

CINA

;Wait till character ready

0006

DB12

IN

PORTA+UDAT

; Read character

8000

E67F

ANI

7FH

; Mask off top bit

A000

C9

RET

000B

000B

DB13

COUTA

IN

PORTA+USTA

; Check USART status

000D

E601

ANT

;Get TxReady bit

000F

28FA

JRZ

COUTA

;Wait till ready

0011

78

VOM

A,B

;Output char is in B req

0012

D313

OUT

PORTA+USTA

;Output character

0014

C9

RET

0015

;

0015

0015

; Port B input and output routines

0015

0015

DB17

CINB

IN

PORTB+USTA

; Check USART status

0017

E602

ANI

2

;Get RxReady bit

0019

;Wait till character ready

28FA

JRZ

CINB

001B

DB16

IN

PORTB+UDAT

; Read character

001D

E67F

ANI

7FH

; Mask off top bit

001F

C9

RET

0020

0020

COUTB

DB17

IN

PORTB+USTA

; Check USART status

0022

E601

ANI

1

; Get TxReady bit

0024

28FA

JRZ

COUTB

;Wait till ready

0026

78

VOM

A,B

;Output char is in B reg

0027

D317

OUT

PORTB+USTA

;Output character

0029

C9

RET

002A

```

```

002A

; Port C input and output routines

002A

002A

002A

CINC

PORTC+USTA

; Check USART status

DB1B

TN

;Get RxReady bit

002C

E602

ANI

002E

28FA

JRZ

;Wait till character ready

CINC

;Read character

0030

DB1A

IN

PORTC+UDAT

E67F

; Mask off top bit

0032

ANI

7FH

RET

0034

C9

0035

COUTC

:Check USART status

0035

DB1B

IN

PORTC+USTA

;Get TxReady bit

0037

E601

ANI

0039

28FA

JRZ

COUTC

;Wait till ready

003B

VOM

;Output char is in B reg

78

A,B

003C

D31B

OUT

PORTC+USTA

;Output character

003E

C9

RET

003F

î

003F

003F

; Port D input and output routines

003F

003F

DB1F

CIND

PORTD+USTA

; Check USART status

IN

;Get RxReady bit

0041

E602

ANI

2

0043

28FA

JRZ

CIND

;Wait till character ready

:Read character

0045

DB1E

IN

PORTD+UDAT

0047

E67F

ANI

7FH

; Mask off top bit

0049

C9

RET

004A

COUTD

; Check USART status

004A

DB1F

TN

PORTD+USTA

ANI

;Get TxReady bit

004C

E601

1

004E

28FA

JRZ

COUTD

:Wait till ready

;Output char is in B reg

0050

78

VOM

A,B

D31F

OUT

PORTD+USTA

0051

;Output character

0053

C9

RET

```

```

0054

; HSIO-4 initialization routine

0054

0054

0054

3E01

INIT

MVI

A, BAUDA

OUT

:Set baud rates

0056

D310

PORTA+BAUD

0058

3E01

IVM

A, BAUDB

005A

D314

OUT

PORTB+BAUD

005C

3E01

IVM

A, BAUDC

005E

D318

OUT

PORTC+BAUD

0060

3E01

IVM

A, BAUDD

0062

D31C

OUT

PORTD+BAUD

0064

Interrupt masks are cleared at power up

0064

î

0064

;

0064

3E03

MVI

A,3

; Give USART commands

CALL

USTAT

0066

CD8700

; to reset.

0069

CD8700

CALL

USTAT

006C

A, 40H

3E40

IVM

006E

CD8700

CALL

USTAT

A, OCEH

; Give mode command

0071

3ECE

MVI

0073

CD8700

CALL

USTAT

;2 STOP BITS, 16*CLK,

:Give command.

0076

3E27

IVM

A,27H

USTAT

; CMD: RTS, ER, RXF, DTR, TXEN

0078

CD8700

CALL

007B

CD7E00

CALL

INJNK

;Read junk twice

PORTA+UDAT

007E

DB12

INJNK

IN

0800

DB16

IN

PORTB+UDAT

0082

DB1A

IN

PORTC+UDAT

0084

DBlE

IN

PORTD+UDAT

0086

C9

RET

0087

USTAT

0087

D313

OUT

PORTA+USTA

Output command to

0089

D317

OUT

PORTB+USTA

;All HSIO-4 channels

008B

D31B

OUT

PORTC+USTA

008D

D31F

OUT

PORTD+USTA

RET

008F

C9

0090

0090

END

```

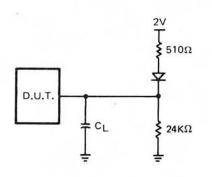

## 3.2.5 CURRENT LOOP OPERATION

Most computers, terminals, and printers use RS-232 signal levels. A few commercially used terminals, such as teletypes, use 20 mA current loop signals.

A teletype is a passive device; it does not supply current, but relies on current supplied by the HSIO-4. The HSIO-4 is not equipped to communicate with active current loop devices such as computers that produce current loop signals.

As supplied, each HSIO-4 port is configured to use RS-232 signals. To configure an HSIO-4 port for current loop operation:

Install a mini-jump at the current loop jumper area for the relevant port. See Table 3-4 below.

Table 3-4

#### CURRENT LOOP JUMPER AREAS

| Port | <u>Jumper Area</u> |

|------|--------------------|

| A    | JP5                |

| В    | JP6                |

| C    | JP7                |

| D    | JP8                |

| <br> |                    |

2. Ensure that the original Configuration Header is in place. The pins should be connected as follows:

pin 1 to pin 16 pin 2 to pin 15 pin 3 to pin 14 pin 4 to pin 13 pin 5 to pin 12 pin 6 to pin 11 pin 7 to pin 10 pin 8 to pin 9

Figure 3-11

- 3. Remove the 1488 for the port and replace it with a header constructed as follows:

- a. Connect a 2N3904 transistor to the 14-pin header with the E lead connected to pin 7, the B lead connected to pin 5, and the C lead connected to pin 6.

- b. Solder a 5.6K ohm 1/4 Watt resistor (green-blue-red) between pin 4 and pin 12 on the header.

- c. Solder a 1K ohm 1/4 Watt resistor (brown-black-red) between pin 8 and pin 14 on the header.

- 4. Connect a 25-pin D-type connector to the terminal cable as follows:

pin 9 to the printer "+" lead pin 3 to the printer "-" lead pin 2 to the keyboard "+" lead pin 10 to the keyboard "-" lead

## 3.2.6 BUFFER FULL SIGNALS

The HSIO-4 supports printers that indicate buffer full status on pin 20 (DTR) or on pin 19 (SCA). Consult the manual for your printer to determine which pin it uses to indicate buffer full status. Depending upon the maufacturer, this signal may be identified as "Printer Ready" or "Buffer Full." The HSIO-4 expects this signal to be high when it is required to send characters and low when it is required to wait.

As supplied, the HSIO-4 expects the buffer full signal on pin 20. Some printers, however, use pin 19. Printers using pin 19 require the following modification to the HSIO-4 board:

1. Locate the 3-pin jumper area to the right of the connector for the port to be modified. (See Table 3-5 below).

Table 3-5

BUFFER FULL JUMPER AREAS

| Port | Jumper Area |

|------|-------------|

| Α    | JP1         |

| В    | JP2         |

| C    | JP3         |

| D    | JP4         |

| 7.5  | 3           |

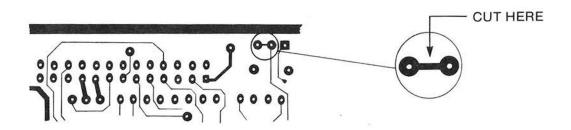

2. Turn the board over so the solder side faces up, and cut the trace that connects the center pin and pin #2 (See Figure 3-12).

Figure 3-12

3. On the component side of the board,

install a mini-jump between the center pin and

pin #1. (The pin numbers are printed on the

component side of the board.)

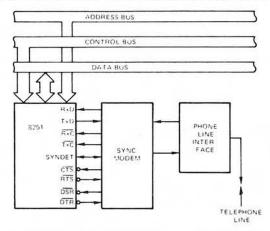

## 3.3 SYNCHRONOUS OPERATION

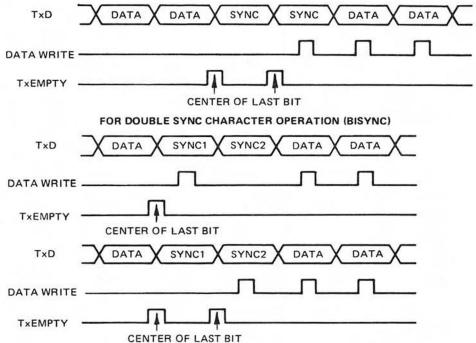

Used primarily to facilitate rapid data communication between two computers, synchronous transmission is also used to communicate with devices that are capable only of synchronous operation, such as high-speed modems.

During synchronous operation, data transmission is synchronized and controlled by equally spaced clock signals. The clock signal is generated by the transmitting port and then used by the receiving port. The timing of the clock signal (and speed at which the sending port transmits data) is determined by the baud rate setting for that port. Thus, the baud rate for both the transmitting port and the receiving port is determined by the baud rate selected at the transmitting end.

As supplied, all four HSIO-4 ports are configured for asynchronous operation. Each port can be reconfigured for synchronous operation (see Sections 3.3.1. and 3.3.2). Sections 3.3.3 and 3.3.5 provide examples of how to program synchronous operation.

Each HSIO-4 port may be configured for synchronous operation in one of two possible ways:

FIXED BAUD RATE (55.8KHz)

The first method allows a synchronous port to transmit at a single fixed baud rate of 55.8KHz, which is the maximum possible synchronous speed provided on the HSIO-4. This method requires two configuration changes, which effect only the modified port.

PROGRAMMABLE BAUD RATES

The second method permits a synchronous port

to use any one of five programmable baud

rates ranging from 1.76KHz to 38.4KHz. A

programmable 55.8KHz baud rate is also

possible, but requires an additional jumper

change, which effects all four ports.

## 3.3.1 FIXED BAUD RATE OF 55.8KHz

To configure an individual port for synchronous operation at a single fixed baud rate of 55.8KHz, make the following changes:

Please Note: At the same time that a port is configured for synchronous operation, it must also be configured to simulate either a modem or a terminal. To determine whether your particular application requires the MODEM or TERMINAL configuration, consult Section 3.1.1.

# 3.3.1 A CONFIGURING PORT AS MODEM (FIXED BAUD RATE)

Disconnect the links between pins 7 and 10 and between pin 8 and 9 on the Configuration Header.

Figure 3-13

Take an 8-pin shunt and install it, with all four links connected (as shown in Figure 3-14), in the Clock Header socket.

Figure 3-14

# 3.3.1 B CONFIGURING PORT AS TERMINAL (FIXED BAUD RATE)

Wire a 16-pin header as follows, and install it in the Configuration Header socket.

pin 1 to pin 2 pin 3 to pin 4 pin 5 to pin 6 pin 11 to pin 12 pin 13 to pin 14 pin 15 to pin 16

Figure 3-15

Wire an 8-pin header as follows, and install it in the Clock Header socket.

pin 1 to pin 2 pin 3 to pin 6 pin 4 to pin 5 pin 7 to pin 8

Figure 3-16

## 3.3.2 PROGRAMMABLE BAUD RATES

To configure an individual port for synchronous operation with programmable baud rates, make the following changes:

Please Note: When a port is configured for synchronous operation, it must also be configured to simulate either a MODEM or a TERMINAL. (To determine whether your particular application requires the MODEM or TERMINAL configuration, consult Section 3.1.1.)

# 3.3.2 A CONFIGURING PORT AS MODEM (PROGRAMMABLE BAUD RATES)

Disconnect the link between pins 8 and 9 on the Configuration Header.

Figure 3-17

Take an 8-pin shunt, disconnect the link between pin 3 and pin 6, and install it in the Clock Header socket.

Figure 3-18

Refer to Section 3.3.3 for instructions on programming baud rates for synchronous operation.

# 3.3.2 B CONFIGURING PORT AS TERMINAL (PROGRAMMABLE BAUD RATES)

Wire a 16-pin header as follows, and install it in the Configuration Header socket.

pin 1 to pin 2 pin 3 to pin 4 pin 5 to pin 6 pin 7 to pin 10 pin 11 to pin 12 pin 13 to pin 14 pin 15 to pin 16

Figure 3-19

Wire an 8-pin header as follows, and install it in the Clock Header socket.

pin 1 to pin 2 pin 4 to pin 5 pin 7 to pin 8

Figure 3-20

Refer to Section 3.3.3 for instructions on programming baud rates for synchronous operation.

### 3.3.3 PROGRAMMING BAUD RATES

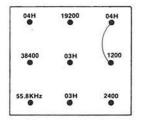

When configured for synchronous operation with programmable baud rates, an HSIO-4 port can transmit data at any one of five programmable baud rates. See Table 3-6 below. An additional jumper change enables three additional programmable baud rates. (For specific instructions, see Section 3.3.4.)

During synchronous operation, the baud rate of the receiving port is determined by the clock signal generated by the transmitting port. Thus, each HSIO-4 baud rate selection determines only the transmission speed for a particular port -- not the receiving speed.

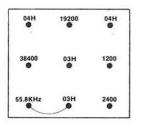

Table 3-6

PROGRAMMABLE SYNCHRONOUS BAUD RATES

| Output<br><u>Value</u> | Standard | Alternatives (With Jumper Change) |  |  |

|------------------------|----------|-----------------------------------|--|--|

| 00H                    | Not Used |                                   |  |  |

| 01H                    | Not Used |                                   |  |  |

| 02H                    | Not Used |                                   |  |  |

| 03H                    | 38400    | 19200 or 2400 or 1200 or 55.8K    |  |  |

| 04H                    | 19200    | 38400 or 1200                     |  |  |

| 05H                    | 9600     |                                   |  |  |

| 06H                    | 4800     |                                   |  |  |

| 07H                    | 1760     |                                   |  |  |

Please Note: Output values 00H, 01H and 02H cannot be used in synchronous mode as they exceed USART speed capabilities.

The baud rate for each port is programmed independently. To program the desired baud rate for a port, output the Output Value (from Table 3-6) to the Baud Rate Select Address for the relevant port.

To determine the Baud Rate Select Address, consult Table 3-1 (in Section 3.1.3).

For example, assuming the HSIO-4 board is addressed starting at 10H, you would set the baud rate to 4800 on port B by outputting 06H (the Output Value) to I/O address 14H with the following instructions:

0000 3E06 0002 D314 MVI A,6; Output Value for 4800 Baud Sync. OUT 14H

The baud rate must be selected BEFORE executing software instructions to set up the USART for synchronous transmission.

# 3.3.4 ALTERNATIVE BAUD RATES (REQUIRED JUMPER CHANGES)

The baud rates listed in Table 3-6 as "Alternatives (With Jumper Change)" can be made available as described below. Please Note: Such a jumper change effects all four HSIO-4 ports.

- Locate JP13, turn the board so that the solder side faces up, and cut one of the traces as directed below.

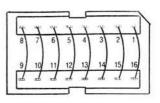

- A. To implement one of the baud rates for Output Value 03H:

Cut the bottom trace, as shown in Figure 3-22. Then turn the board so that the component side faces up, and install a mini-jump between the pin marked with the speed you wish to specify and the nearest pin marked "03H." Figure 3-21, for example, shows where to install the mini-jump to specify 55.8KHz.

Figure 3-21

Figure 3-22

B. To implement one of the baud rates for Output Value 04H:

Figure 3-23

Cut the top trace, as shown in Figure 3-22. Then turn the board so that the component side faces up and install a mini-jump between the pin marked with the speed you wish to specify and the nearest pin marked "04H." Figure 3-23, for example, shows where to install the mini-jump to specify 1200 baud.

#### 3.3.5 SAMPLE PROGRAM

This section provides a very basic example of how to program a USART in the HSIO-4 for synchronous operation. Programming for specific applications requires a detailed familiarity with USART operation. It is beyond the scope of this manual to provide specific instructions on programing for such applications. However, for the convenience of the programmer, the manufacturer data sheet for the USART is reproduced in Appendix B.

Three routines are given:

INIT sets up the USART in synchronous mode, waiting to receive sync characters.

SYNI loads a received message into RAM starting at the address given in HL.

SYNO transmits a message from RAM starting at the address given in HL. The message length (number of bytes) is given in BC. The message is preceded by 255 DLE-SYN sync character pairs and a DLE-STX; this indicates the start of the message. The message is terminated by a DLE-ETX; this indicates the end of the message.

As the data transferred is binary and may contain any character, an escape character must be used to indicate the presence of control characters such as End-of-text, Start-of-text, and Sync. The escape character used here is DLE (10H). If a DLE character occurs in the data, this is replaced by two DLEs in sequence.

```

; Sample routines to use HSIO-4 for synchronous operation

0000

0000

0000

STX

EQU

2

; Start of text character

0002

; End of text character

3

ETX

EOU

0003

; Data Link Escape character

0010

DLE

EQU

10H

SYN

EQU

16H

; Sync character

0016

0000

TXRDY

EOU

1

; USART status bits

0001

2

0002

RXRDY

EQU

0000

; Set for HSIO-4 port A

PORTA

EOU

10H

0010

EOU

; Baud rate for port A

BAUD

PORTA

0010

EQU

PORTA+2 : USART data address

0012

DATA

CTRL

PORTA+3 ; USART control/status

EQU

0013

0000

0000

; Set data rate to 2400*16

0000

3E03

INIT

IVM

A,3

; for HSIO-4

0002

D310

OUT

BAUD

; Ensure USART is cleared

A,80H

0004

3E80

IVM

D313

OUT

CTRL

; as specified by manufacturers

0006

CTRL

OUT

8000

D313

A,40H

; do reset

000A

3E40

IVM

D313

OUT

CTRL

000C

000E

î

3E0C

MVI

A, OCH

; Double sync, no parity

000E

0010

D313

OUT

CTRL

; Sync character #1

A, DLE

0012

3E10

IVM

CTRL

0014

D313

OUT

0016

3E16

IVM

A, SYN

; Sync character #2

0018 D313

OUT

CTRL

; Hunt, RTS, Error reset, RxE, DTR, TxE

001A

3EB7

IVM

A,0B7H

CTRL

001C

D313

OUT

DATA

; Read junk

001E

DB12

IN

0020

C9

RET

```

```

0021

; Synchronous input routine (RAM address in HL)

0021

0021

0021

CD0000

SYNI

CALL

INIT

; Set USART into hunt mode and

CALL

GETCH

: reset errors

0024

CD5100

CPI

0027

FE10

DLE

0029

20F6

JRNZ

SYNI

; Wait for DLE to appear

GETCH

002B

CD5100

CALL

002E

CPI

; If SYNC, try again

FE16

SYN

0030

28EF

JRZ

SYNI

0032

FE02

CPI

STX

; Check for start of text,

0034

20EB

JRNZ

SYNI

; if bad, try again

0036

; Transfer message into RAM

0036

0036

SDATA

0036

CD5100

CALL

GETCH

0039

FE10

CPI

DLE

003B

2010

JRNZ

RAMLD

; If not DLE then data

003D

CD5100

CALL

GETCH

; Get second char of DLE seq

; If DLE-DLE then use one

0040

FE10

CPI

DLE

RAMLD

; of them as data

0042

2809

JRZ

0044

FE16

CPI

; Check for padding (SYNC chars)

SYN

; ignore if it is

0046

28EE

JRZ

SDATA

0048

FE03

ETX

; End yet ?

CPI

004A

C8

RZ

; If not done, then bad DLE

004B

18E9

JR

SDATA

; sequence found, ignore it

004D

RAMLD

MOV

; Insert byte into RAM at (HL)

004D

77

M,A

004E

23

INX

H

004F

18E5

SDATA

; Get next byte

JR

0051

GETCH

0051

DB13

IN

CTRL

; Get char from serial port

0053

E602

ANI

RXRDY

; Wait till done

0055

28FA

JRZ

GETCH

0057

DB12

IN

DATA

0059

C9

RET

```

```

005A

005A

; Synchronous output routine

; Outputs BC characters starting at address in HL

005A

005A

; Reset USART

CD0000

SYNO

CALL

INIT

005A

; Save byte count

C5

PUSH

В

005D

; Send 255 DLE-SYNCs

IVM

B, 0

005E

0600

0060

3E10

HEADR

IVM

A, DLE

; before message

CALL

OPCH

0062

CD9100

A, SYN

0065

3E16

IVM

OPCH

0067

CD9100

CALL

HEADR

006A

10F4

DJNZ

C1

POP

; Restore byte count

006C

006D

î

; Send message header of

006D

3E10

IVM

A, DLE

: DLE STX

006F

CD9100

CALL

OPCH

MVI

A,STX

0072

3E02

CD9100

CALL

OPCH

0074

0077

Transfer message contents

0077

0077

7E

NCHO

VOM

A,M

0077

CD9100

OPCH

; Output byte of data

0078

CALL

; DLE for comparison

IVM

A, DLE

007B

3E10

; Check if char was DLE and count

CPII

007D

EDAl

CC9100

OPCH

; Output second DLE if it was

007F

CZ

0082

EA7700

JPE

NCHO

; Loop till done

CD9100

CALL

OPCH

; Output DLE from A

0085

; Send End of text

IVM

0088

3E03

A, ETX

CD9100

CALL

OPCH

A800

; Stop SYNC characters

008D

CD0000

CALL

INIT

0090

RET

; Return to calling program

C9

0091

; Output Character

0091

F5

OPCH

PUSH

PSW

; Get USART status

0092

DB13

XTW

IN

CTRL

ANI

TXRDY

; Check if ready for character

0094

E601

; Wait till it is

WTX

0096

28FA

JRZ

; Get character back and

0098

POP

PSW

Fl

0099

OUT

DATA

; output

D312

009B

C9

RET

009C

ï

009C

END

```

Each HSIO-4 port provides four sources of interrupt from the following signals:

### Table 3-7

#### INTERRUPT SIGNALS

| Signal                     | Function                                                                                                                              |  |  |  |  |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Tx Empty Tx Ready Rx Ready | Transmitter has finished sending characters<br>Transmitter is ready for next character<br>Receiver has a character ready for computer |  |  |  |  |

| Sync Detect                | Synchronization has been achieved (in synchronous mode only)                                                                          |  |  |  |  |

The first three interrupt sources are armed and disarmed under program control; the fourth interrupt source, Synchronous Detect, is armed by a mini-jump on the HSIO-4 board. The resultant interrupt from each port can be connected to any of the S-100 interrupt lines. As supplied, the interrupts for all HSIO-4 ports are connected to S-100 bus interrupt line VI2.

## 3.4.1 ARMING AND DISARMING MASKABLE INTERRUPTS

To arm maskable interrupts for a port, set the particular bit(s) in the mask that corresponds to the interrupt -- or combination of interrupts -- you wish to use. This is done by outputting the value for the required bit pattern to the Interrupt Mask Set I/O address for the relevant port.

As shown in Table 3-9, there are a total of eight possible bit patterns. When output to the Interrupt Mask Set address for a particular port, the bit pattern establishes the status (arm/disarm) of all three maskable interrupts for that port. Table 3-9 shows the values that correspond to each of the eight possible bit patterns. Table 3-1 shows the Interrupt Mask Set addresses for each port.

For example: Assuming that the HSIO-4 board is addressed starting at 10H, to arm the Tx Ready interrupt (and disarm the other two interrupts) for Port C, you would output 02H to I/O address 19H (the Interrupt Mask Set I/O Address for Port C).

Similarly, to disarm all three maskable interrupts for port C, you would output 00H to I/O address 19H.

Table 3-8 INTERRUPT MASK BIT ALLOCATION

| <u>Value</u> | Bit | Signal   | Function                                            |

|--------------|-----|----------|-----------------------------------------------------|

| 1            | 0   | Tx Empty | Transmitter has finished sending characters         |

| 2            | 1   | Tx Ready | Buffer is ready to receive the next character       |

| 4            | 2   | Rx Ready | Receiver has a character to be read by the computer |

Bit 0 is the least significant bit.

All interrupt mask bits are disarmed when the computer is powered up or reset.

Table 3-9

1 = Arm0 = Disarm

## EIGHT POSSIBLE BIT PATTERNS

| <u>Value</u> | Rx Ready | Tx Ready | Tx Empty |  |  |

|--------------|----------|----------|----------|--|--|

|              |          |          |          |  |  |

| 00H          | . 0      | 0        | 0        |  |  |

| 01H          | 0        | 0        | 1        |  |  |

| 02H          | 0        | 1        | 0        |  |  |

| 03H          | 0        | 1        | 1        |  |  |

| 04H          | 1        | 0        | 0        |  |  |

| 05H          | 1        | 0        | 1        |  |  |

| 06H          | 1        | 1        | 0        |  |  |

| 07H          | 1        | 1        | 1        |  |  |

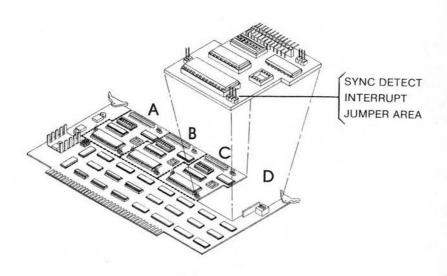

# 3.4.2 ARMING THE SYNCHRONOUS DETECT INTERRUPT

As supplied, the Synchronous Detect interrupt for each HSIO-4 port is disarmed. The Synchronous Detect interrupt can be armed by a mini-jump.

To arm a Synchronous Detect interrupt:

1. Locate the 3-pin jumper area to the right of the USART for the relevant port, and install a mini-jump between the center pin and pin 2.

Figure 3-24

# 3.4.3 CONNECTING THE INTERRUPT LINES

The HSIO-4 board provides access to ten S-100 bus interrupt lines. These can cause eight vectored interrupts (VIO - VI7), a non-vectored interrupt (PINT), and a non-maskable interrupt (NMI).

Each port provides four sources of interrupt. The four interrupt sources from each port are combined into a single interrupt source for each port. These combined interrupt sources — one for each port — are brought to the Interrupt Header. As shown in Figure 3-25, the interrupt sources for ports A, B, C, and D are made available on pins 1, 2, 3, and 4, respectively.

Figure 3-25

Any one or more of these combined interrupt sources can be connected to an S-100 interrupt line at the Interrupt Header. The specific connections to be made are determined by the particular software in use; consult the manual for the software you intend to use. If you are writing your own software, it is recommended that you utilize the standard Interrupt Header wiring with which the HSIO-4 is supplied. This wiring is illustrated in Figure 3-27.

To connect the interrupt sources to the S-100 interrupt lines:

- 1. Take a 14-pin header and wire the interrupt source for the desired port(s) to the pin carrying the required interrupt line.

- 2. Install this header in the Interrupt Header Socket (Location 2F).

For example, to cause all sources of interrupt from Port A to generate Vectored Interrupt 2 (VI2), you would wire pin 1 to pin 12 on a 14-pin header, as shown below:

Figure 3-26

As supplied, the interrupts for each HSIO-4 port are all wired to S-100 bus interrupt line VI2, as shown in Figure 3-27.

Figure 3-27

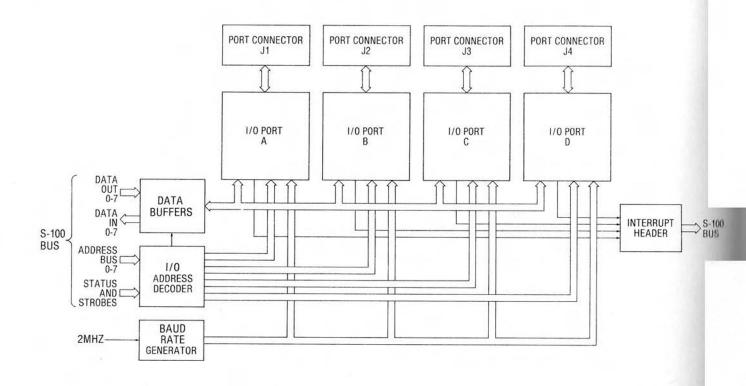

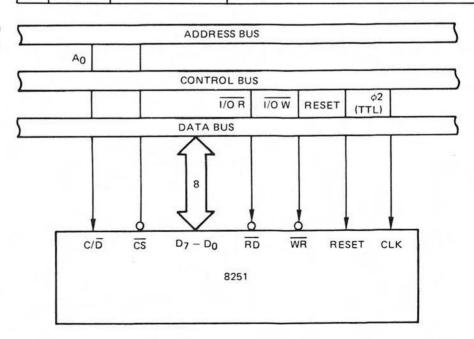

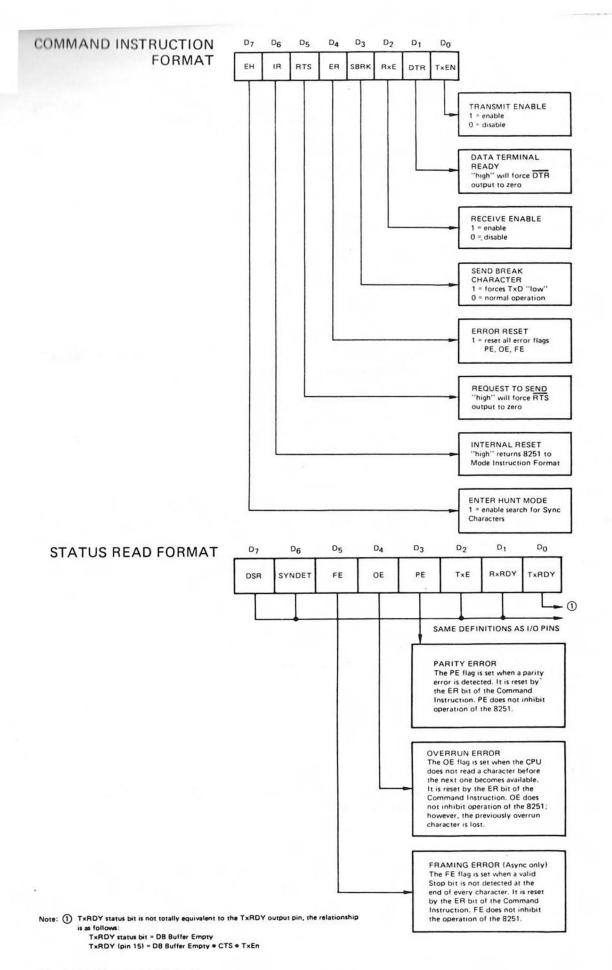

The HSIO-4 board consists of four independent serial I/O ports, and some common control logic. The major common functional blocks are the I/O Address Decoder, the Data Buffers, the Baud Rate Generator, and the Interrupt Header. (See Figure 4-1.)

FUNCTIONAL BLOCK DIAGRAM OF THE HSIO-4

Figure 4-1

## 4.1 ADDRESS DECODER

The Address Decoder converts I/O address and. timing signals from the processor into a set of signals for each of the four I/O ports.

The HSIO-4 board is selected by address bits A4 - A7. These address bits are compared with the address switches. If a match occurs, the board is selected. Address bits A0 - A3 select functions within the board. Address bits A2 and A3 select one of the four I/O ports as follows:

| <u>A3</u> | A2 |         |      |   |

|-----------|----|---------|------|---|

| 0         | 0  | Selects | Port | A |

| 0         | 1  | Selects | Port | В |

| 1         | 0  | Selects | Port | C |

| 1         | 1  | Selects | Port | D |

Address bits AO and Al select the operation to be performed by the selected port as follows:

| <u>A0</u> | Al |                                       |

|-----------|----|---------------------------------------|

| 0         | 0  | Write to Baud Rate Select Register    |

| 0         | 1  | Write to Interrupt Mask Register      |

| 1         | 0  | Write or read USART data              |

| 1         | 1  | Write or read USART control or status |

### 4.2 DATA BUFFERS

The Data Buffers interface the S-100 bus Data Out (DO) and Data In (DI) lines to a single bidirectional bus on the HSIO-4. During S-100 bus writes, the Data Buffers gate data from the S-100 DO bus onto the HSIO-4 internal bus. During USART reads, the buffers gate the read data onto the S-100 DI bus.

### 4.3 BAUD RATE GENERATOR

Each of the four ports can be programmed to select one of eight baud rates. These eight baud rates are derived from eleven frequencies produced by the Baud Rate Generator as shown in Table 4-1:

|        | Tabl | .e | 4-1    |   |                                         |  |

|--------|------|----|--------|---|-----------------------------------------|--|

| 1760   | Hz c | -  | (110   |   | 000000000000000000000000000000000000000 |  |

| 4800   | Hz c | r  | (300   | X | 16)                                     |  |

| 9600   | Hz c | r  | (600   | X | 16)                                     |  |

| 76800  | Hz o | r  | (4800  | X | 16)                                     |  |

| 153600 | Hz o | r  | (9600  | X | 16)                                     |  |

| 307200 | Hz o | r  | (19200 | x | 16)                                     |  |

| 610    | Hz o | r  | (75    | x | 16)                                     |  |

| 1220   | Hz o |    | (150   |   |                                         |  |

| 19200  | Hz o | r  | (1200  | x | 16)                                     |  |

| 38400  | Hz o | r  | (2400  | x | 16)                                     |  |

| 55800  | Hz   |    |        |   |                                         |  |

|        |      |    |        |   |                                         |  |

The first six frequencies go directly to the I/O ports. Of the next four frequencies, only two go to the I/O ports. The two frequencies that are allowed to go to the I/O ports for program selection are selected by mini-jumps at JP13. The eleventh frequency (55800 Hz) can be selected by a mini-jump at JP13. When selected, this frequency goes directly to all four Clock Headers.

58

## 4.4 INTERRUPT HEADER

The USART in each I/O port generates four flags which, under software and hardware control, can generate an interrupt signal. The selected flags are ORed together within each I/O port. These four signals, one from each I/O port, are brought to the Interrupt Header.

The Interrupt Header can be wired to connect the interrupt signals to any of the S-100 bus interrupt lines. More than one I/O port interrupt signal may be connected to one S-100 bus interrupt line. As supplied, all four port interrupt signals are connected to the S-100 bus interrupt VI2.

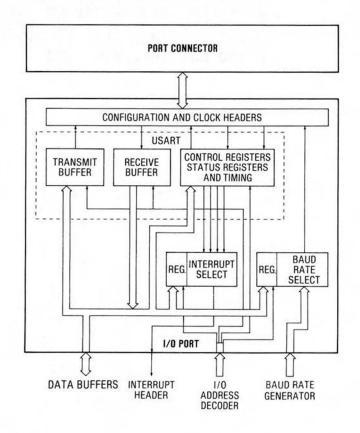

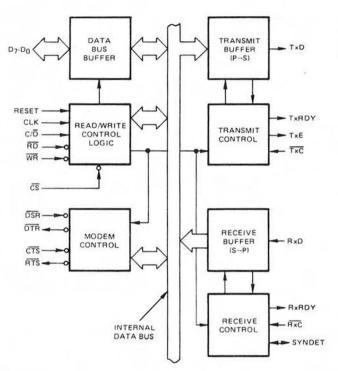

Each I/O port contains a USART, Configuration and Clock Headers, a Baud Rate Select Register, and an Interrupt Select Register. (See Figure 4-2.)

FUNCTIONAL BLOCK DIAGRAM OF AN INDIVIDUAL I/O PORT

Figure 4-2

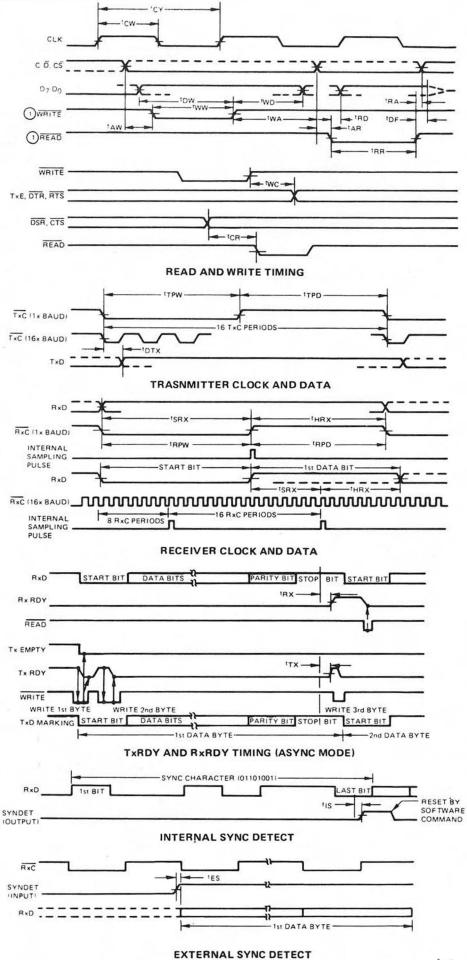

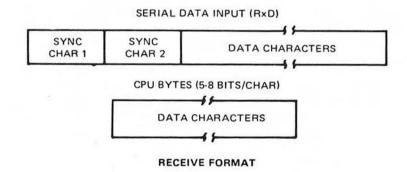

4.5.1 USART

> USART is an acronym for Universal Synchronous/Asynchronous Receiver/Transmitter. The USART can be programmed from the processor to communicate in most commonly used types of serial data transmission. The USART receives serial data streams and converts them into parallel data bytes for input to the processor. While receiving serial data, the USART will also accept data bytes from the processor in parallel format, convert them to serial format and transmit them. By performing conversion and formatting services automatically, the USART appears to the processor as a simple device for input or output of byte-oriented parallel data. A control register within the USART determines parameters. A complete USART status byte, including data format, error and status signals such as Transmitter Empty, Transmitter Ready, and Synchronous Detect, is available to the processor at any time. For the convenience of users requiring more detailed information, a manufacturer data sheet for the USART is reproducd in Appendix B, along with notes on the Interface to the USART.

# 4.5.2 CONFIGURATION AND CLOCK HEADERS

Various connections on the Configuration Header and the Clock Header for a port permit several types of serial transmission. The header configurations determine how the USART connects to the port connector and the baud rate signals.

## 4.5.3 BAUD RATE SELECT REGISTER

Each I/O port has a three-bit Baud Rate Select Register, which selects the baud rate. Physically, each bit is in a different IC (Locations 5F, 5E, and 5D). Logically, the Baud Rate Select Register is a single register loaded from the three least significant data bits of an output instruction from the processor. This register selects one of the eight frequencies to be sent to the Configuration Header.

To use the 55800 Hz signal, the Configuraton and Clock Headers can be wired to use the 55800 Hz signal ONLY and not the selectable rates.

# 4.5.4 INTERRUPT SELECT REGISTER

Each port has a three-bit Interrupt Select Register. Physically, each bit is in a different IC (Locations 5F, 5E, 5D).

Logically, the Interrupt Select Register is a single register loaded from the three least significant data bits of an output instruction from the processor. Each bit in the register controls the arming/disarming of one flag from the USART. Only if a flag is armed is it ORed into the interrupt signal for the I/O port.

Bit 0 arms the TRANSMIT EMPTY SIGNAL Bit 1 arms the TRANSMIT READY SIGNAL Bit 2 arms the RECEIVE READY SIGNAL

The Synchronous Detect Flag, which is armed by a mini-jump, is only used for synchronous transmission.

If you lose communication with any peripheral device connected to the HSIO-4 board, you must first determine whether the cause of the failure is in a specific peripheral device and its cabling to the computer or in the HSIO-4 board itself.

Use the following procedure to trace the cause of a communications failure:

- If peripheral devices are connected to more than one I/O port and communication to all the connected peripherals has failed, this indicates that some part of the HSIO-4 not specific to a particular I/O port may be at fault. In this case, follow the procedure outlined in Section 5.3.

- 2. If you lose communication with only one peripheral, you should check that the configuration of the peripheral and the cable connection to the computer have not been altered. Make sure the connectors at both ends of the cable are firmly seated. Retry establishing communication with the peripheral.

- 3. If communication with the peripheral is still lost, disconnect the cable from the malfunctioning port, re-connect it to one of the other I/O ports that is functioning properly, and retry establishing communication through the new I/O port.

- 4. If communication is still lost, this indicates that the problem is with the peripheral device itself or the connecting cable.

- 5. If communication is successfully established, this indicates that some part of the HSIO-4 board specific to the I/O port first tested is at fault. Follow the procedures in Sections 5.1 and 5.2.

## 5.1 CREATING A TEST DISKETTE

Before testing an individual I/O port, you must create a test diskette. The procedure for creating such a test diskette is described in Sections 5.1.1 - 5.1.3 below. This procedure utilizes a feature, supported by DOS and BASIC, known as "auto-start," which automatically loads BASIC and runs the HSIO-4 test. Once a test diskette has been set up, restarting the computer with the reset switch prompts DOS to load BASIC, which, in turn, starts the HSIO-4 test.

# 5.1.1 CREATING AN AUTO-START DOS DISKETTE

To create an auto-start DOS diskette:

- Make a copy of the North Star DOS and BASIC diskette (version 5.2 and up).

- Put the copy of the DOS and BASIC diskette in drive one and restart the computer with the reset switch.

- 3. Type: GO BASIC

- 4. Type the following commands:

- 10 OPEN #1 %0,"DOS"

- 20 WRITE #1 %48,&0,NOENDMARK

- 30 CLOSE #1

RUN

5. Restart the computer with the reset switch. The word READY should appear on the screen, indicating that auto-start of BASIC has been successfully established.

## 5.1.2 CREATING THE TEST PROGRAM

- Type in the BASIC program that is listed on the next page. In order to simplify the program entry, delete the REMark statements (which have been added only to explain the test process).

- List the program to verify that it has been correctly entered into BASIC.

- 3. Save this test program on the diskette by typing: NSAVE HSIOTEST

```

HSIOTEST 8-April-81

11 REM PROGRAM NAME=

12 !TAB(10), "North Star HSIO-4 Test" \!

13

REM Set up port addresses for first HSIO-4 port--

14

REM Edit B for non-standard address!

15 B=16

\REM Base address of HSIO-4 =10 hex.

16 D=B+2

\REM USART data port address.

17 C=D+1

\REM USART command port address.

REM set HSIO-4 baud rates--

18

19 FOR P=B TO B+12 STEP 4

OUT P,1

20

\REM 1=9600 baud, 4=1200 baud.

21 NEXT P

\REM P= baud rate select address.

2.2

REM initialize the USARTs--

23 FOR A=1 TO 5

\REM Send 5 bytes of ...

24

READ N

\REM initialization code to...

FOR P=C TO C+12 STEP 4

25

\REM each command port.

26

OUT P, N

27

NEXT P

28 NEXT A

29

REM Clear each HSIO-4 port--

30 FOR P=D TO D+12 STEP 4

X = INP(P)

\REM clear by reading each data port.

31

32 NEXT P

33 !\!"(note: connect pin 2 to pin 3 on the port to be tested!)"\!\!

34 ! CHR$(13), "Test port [A,B,C,D]: ", \T$=INCHAR$(0) \!\!

35 IF T$>="A" THEN IF T$<="D" THEN 36 \GOTO 34

36 !"Press <ESC> to abort current test..." \!\! \!"Testing port: ",T$

37 P=4*(ASC(T$)-64)-2+B

\REM Convert ASCII 'A', 'B', 'C', 'D'...

38

REM into actual data port address...

39

REM (B+2, B+6, B+10, B+14).

40

z=0

\REM Initialize error counter.

\REM Test all possible bytes.

41

FOR T=0 TO 255

PRINT ".",

42

\REM Show some life!

43

X=INP(P+1) \setminus IF INT(X*.5)*2 = X THEN 43 \setminus REM Wait until port ready.

44

\REM Send it a character.

45

FOR I=1 TO 50 X=INT(INP(P+1) *.5)

46

IF INT(X*.5)*2<>X THEN EXIT 50 \REM Exit if character received.

47

NEXT

48

!CHR$(7), "Input status not ready. Not receiving data!"

49

GOTO 53

50

R = INP(P)